打开微信,点击底部的“发现”,

使用 “扫一扫” 即可将网页分享到我的朋友圈。

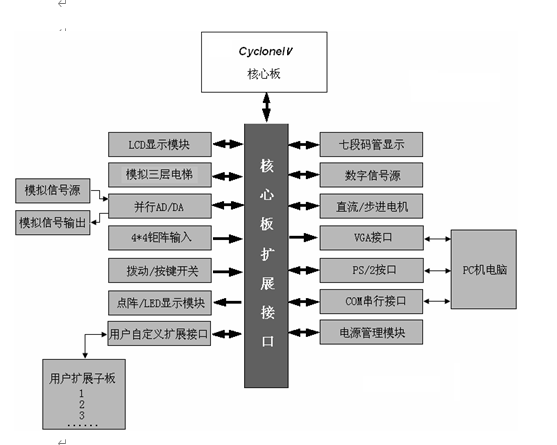

FPGA实验开发系统是结合目前市面上以及实际应用需要,同时兼顾入门学生以及资深开发工程师的应用需求而研发的。就资源而言,它已经涵盖了基础模块、控制类模块、通信类、单片机控制等方面的内容。

支持以下实验:

实验一 基于QUARTUSII图形输入电路的设计

实验二 基于VHDL格雷码编码器的设计

实验三 含异步清零和同步使能的加法计数器

实验四 八位七段数码管动态显示电路的设计

实验五 数控分频器的设计

实验六 图形和VHDL混合输入的电路设计

实验七 基本触发器的设计

实验八 可控脉冲发生器的设计

实验九 基于VHDL的抢答器的设计

实验十 基于VHDL的表决器的设计

实验十一 正负脉宽调制信号发生器设计

实验十二 矩阵键盘接口电路的设计